Sejarah Penemuan Gerbang Logika

Pada tahun 1854 George Boole menciptakan logika simbolik yang sekarang dikenal dengan aljabar Boole. Setiap peubah (variabel) dalam aljabar Boole hanya memiliki dua keadaan atau dua harga, yaitu "keadaan benar" yang dinyatakan dengan " 1 " atau "keadaan salah" yang dinyatakan dengan " 0 "

Kemudian aljabar Boole diwujudkan berupa sebuah piranti atau sistem yang disebut "Gerbang Logika".

Pengertian Gerbang Logika

Gerbang logika adalah blok bangunan dasar untuk membentuk rangkaian elektronika digital, yang digambarkan dengan simbol-simbol tertentu yang ditetapkan.

Sebuah gerbang logika memiliki beberapa masukan tetai hanya memiliki satu keluaran.

Macam-Macam Gerbang Logika Dasar

1. Gerbang Logika OR

2. Gerbang Logika AND

3. Gerbang Logika NOT(INVERTER)

1. Gerbang Logika OR

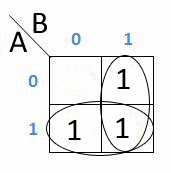

Gerbang Logika OR memiliki dua atau lebih isyarat masukan (input) tetapi hanya memiliki satu isyarat keluaran(output).

Jika salah satu isyarat masukannya 1, maka sinyal keluarannya 1.

Dalam Persamaan aljabar Boole, ditulis dengan : A+B=Y

Lambang Gerbang OR

Tabel Kebenaran Gerbang OR

Gerbang Logika OR dapat dianalogikan dengan model saklar lampu yang dirangkai paralel.

Dengan input A = Low(0) dan Input B=High(1)

Gerbang Logika OR juga dapat dianalogikan sebagai model saluran air yang dipasang paralel.

Model Keran OR

Pemodelan Gerbang Logika OR dengan Dioda.

Model Dioda OR

Bentuk Rangkaian Gerbang Logika OR dengan Dioda.

Gerbang OR dengan 3 Input.

Gerbang OR dengan 3 Input logikanya sama dengan gerbang OR 2 input, dimana jika salah satu input nya 1 maka outputnya akan 1.

Adapun persamaan aljabar boole nya :

A+B+C=Y

Gerbang OR 3 Input

Tabel Kebenaran OR 3 Input

Penerapan Gerbang Logika OR

Gerbang logika OR memiliki Penerapanyang luad dalam bidang elektronika digital, contohnya Encoder dari Decimal ke Biner dan sebagai Kendali/Pengatur dalam Osilator.

Rankaian Encoder

rangkaian osilator OR

Analisis Pewaktuan (Timing Analysis).

Analisis Pewaktuan berguna untuk menganalisis tanggapan output dari sebuah gerbang dan untuk menganalisis pergantian nilai maksimum, dimana cara menganalisisnya disebut dengan Diagram Pwaktuan.

Diagram Pewaktuan sendiri berupa grafik perubahan level keluaran terhadap perubahan level masukan pada waktu tertentu.

Diagram Pewaktuan Gerbang OR

Diagram Pewaktuan OR Dinyatakan dalam Deret Biner

2. Gerbang Logika AND

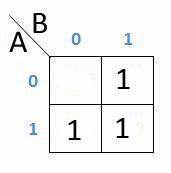

Gerbang logika yang apabila salah satu input nya 0 maka outputnya juga akan 0.

jika kedua input bernilai 1 maka outputnya bernilai 1. Aljabar Boole nya A.B=Y .

Lambang Gerbang AND

Tabel Kebenaran AND

Gerbang Logika AND dapat dianalogikan dengan model saklar lampu yang dirangkai seri.

Model Saklar AND

Tabel Kebenaran Saklar AND

Pemodelan Gerbang Logika AND dengan Dioda.

Model Dioda AND

Gerbang Logika AND dengan 3 Input.

Gerbang logika AND dengan 3 input, logikanya sama dengan 2 input. dimana jika salah satu dari 3 input tersebut nilai nya 0 maka hasilnya akan 0 juga. Aljabar Boole nya : A.B.C=Y

Lambang Gerbang Logika AND 3 Input

Tabel Kebenaran Gerbang Logika AND 3 Input

Analisis Pewaktuan (Timing Analysis) gerbang logika AND.

Diagram Pewaktuan AND

Diagram Pewaktuan AND Dinyatakan Dalam Deret Biner

Penerapan Gerbang Logika AND.

Gerbang Logika AND dapat digunakan sebagai fungsi pengatur atau kendali Enable (mengaktifkan) dan kendali (Disable) (monon-aktifkan) suatu rangkaian elekronik.

Penggunaan Gerbang AND Dalam Osilator

Menggunakan Rangkaian Terpadu atau IC Gerbang-gerbang Logika.

Gerbang Logika AND dan OR tersedia dalam kemasan IC.

Beberapa Daftar IC yang didalamnya terintegrasi Gerbang AND dan OR, diantaranya :

1. 7408 (74HC08)

Kemasan IC yang berisi empat gerbang logika AND,masing-masing memiliki dua input.

2. 7411 (74HC11)

Kemasan IC yang berisi dua gerbang logika AND, masing-masing memiliki tiga input.

3. 7412 (74HC12)

Kemasan IC yang berisi dua gerbang logika AND, masing-masing memiliki tiga input.

4. 7432 (74HC32)

Kemasan IC yang berisi empat gerbang logika OR dua masukan.

Gerbang OR dan AND yang Terintegrasi di Dalam IC

3. Gerbang Logika NOT (INVERTER) ATAU PEMBALIK ATAU COMPLEMENT

Merupakan sebuah gerbang logika yang memiliki satu input dan satu output yang berfungsi sebagai pembalik.

Persamaan aljabar Boole nya ditulis :

Lambang Gerbang Logika NOT

Tabel Kebenaran Gerbang Logika NOT

Pemodelan Gerbang Logika NOT dengan Dioda.

Model Dioda NOT

Analisis Pewaktuan (Timing Analysis) gerbang logika NOT.

Diagram Pewaktuan NOT

Gerbang Logika NOT yang Terintegrasi Dalam IC

Gerbang Logika Inverter Ganda.

Merupakan sebuah gerbang logika NOT yang dipasang 2 buah, sehingga Input pada Gerbang NOT pertama merupakan output gerbang NOT kedua.

Persamaan aljabar Boole untuk inverter ganda ditulis :

NOT ganda dengan input 0 yang dipasang LED

NOT ganda dengan Input 1

NOT ganda dengan input 1 yang dipasang LED

Tabel Kebenaran NOT Ganda